התחלה של תיריסטור

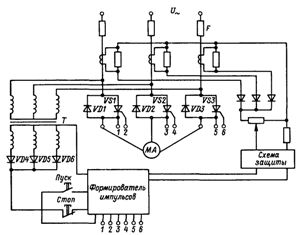

התחלה של תיריסטור הם מכשירים ללא מגע ומשמשים להפעלה וכיבוי של מערכות אלקטרומכניות. בכל שלב של המתנע (איור 1), ללא חסימה תיריסטורים VS1 - VS3 ודיודות VD1 - VD3.

התחלה של תיריסטור הם מכשירים ללא מגע ומשמשים להפעלה וכיבוי של מערכות אלקטרומכניות. בכל שלב של המתנע (איור 1), ללא חסימה תיריסטורים VS1 - VS3 ודיודות VD1 - VD3.

תיריסטורים נפתחים אחת לתקופה ברציפות במרווחי זמן T/3, ברגעי הזמן בהם מופעל דופק לפתיחת התיריסטור, כאשר המתח עובר באפס לכיוון עלייתו בכיוון ההולכה.

לאחר שהמתח מגיע לאפס, התיריסטור הופך ללא מוליך והמתח של אותו שלב מוזן דרך הדיודה המקבילה. לאחר שליש מהתקופה, התיריסטור הבא נדלק, וכן הלאה. זה מספק אספקה רציפה של אנרגיה למקלט, למשל מנוע האינדוקציה MA (איור 1). שימו לב שאין מכשירי קשר במכשיר, יש רק כפתורי "התחל" ו-"עצור".

אורז. 1. סטרטר תיריסטור

פולסים לפתיחת התיריסטורים מסופקים לטרמינלים 1, 2, 3, 4, 5, 6 של פעימת העיצוב, המוזנת על ידי שנאי נפרד T דרך דיודות VD4, VD5 ו-VD6, המבטיחות אספקת פולסים זהים לקוטביות. .כאשר כפתור "התחל" נלחץ, מעצב הדופק והמתנע מופעלים.

הגנת המנוע מסופקת על ידי נתיכים F ומעגל הגנה מפני זרם יתר. שנאים זרם כלולים בכל שלב של המתנע. הזרמים של שלושת השלבים מסוכמים ומומרים למתח. כאשר המתח מוגדר, אם הוא אינו פועל לזמן קצר, דחפי הפתיחה מוסרים והכונן נעצר. לחיצה על כפתור העצור גם מפסיקה את הפולסים.

מחולל דופק מתנע של תיריסטור

לשליטה בתיריסטורים, כלומר ליצור פולסי בקרה בזמנים מתאימים, ניתן להשתמש במכשירים שונים: מכשירים אלקטרומגנטיים עם מגברים ושנאים מגנטיים, התקני תיריסטורים בעלי הספק נמוך, התקני טרנזיסטור ועוד. הנפוצים ביותר הם מעגלי טרנזיסטורים, אחד מהם יילקח בחשבון.

הניהול יכול להתבצע בצורה אופקית או אנכית. בשליטה אופקית, מתח AC יכול להיות מוסט פאזה ('אופקי') על ידי מחליף פאזה, בדרך כלל בין 0 ל-π.

מתחים שמקורם במתגי פאזה, למשל עבור מיישר גשר תלת פאזי שישה מתחים המוזזים על ידי זוויות π / 3 מופעלים על הדרייבר, מה שמייצר פולסי בקרה בעלי משך מספיק.

נפוץ יותר הוא עקרון הבקרה האנכי, בו נוצר דופק הבקרה, למשל, ברגעי השוויון של מתח הבקרה למתח המסור הגובר באופן ליניארי.

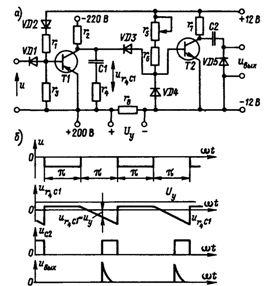

מעגל דומה עבור ערוץ בקרה יחיד של מיישר גל מלא מוצג באיור. 2, א. הקלט מקבל מתח חילופין מעוצב בצורה של פולסים מלבנייםעם רוחב π (איור 2, ב).

אורז. 2. מחולל פעימות מתנע של תיריסטור: א - מעגל לקבלת פולסי בקרה, ב - דיאגרמות זמן של המתחים בצמתים של המעגל

מתח שלילי מסופק דרך הדיודה VD1 לבסיס הטרנזיסטור VT1 במהלך החלק המוליך של התקופה. במרווחי זמן אלו, מתח ur4C1 נמוך יחסית. לאחר הסרת המתח השלילי מבסיס הטרנזיסטור VT1, המתח ur4C1 מתחיל לעלות כמעט באופן ליניארי בהתנגדויות גדולות r2 ו-r4.

כאשר המתח הגובר הזה ur4C1 ישתווה למתח הבקרה Uy, המתח מופיע במוצא הטרנזיסטור VT2. כאשר מבדילים את הדופק הנוכחי במעגל של הטרנזיסטור VT2, נוצר דופק מתח במעגל הבקרה של התיריסטור.

בתרשים המוצג (איור 2, א), הדיודה VD4 משמשת להגבלת המתח השלילי המסופק לבסיס הטרנזיסטור VT2, הדיודה VD3 מונעת את סגירת מקור מתח הבקרה דרך הקבל הפרוק C1 או הטרנזיסטור הרווי VT1, והדיודה VD5 מגבילה את הערך של דופק המוצא.